功率MOSFET

功率MOSFET是專門處理大功率的電壓和電流的金屬氧化物半導體場效電晶體(MOSFET),也是功率半導體的一種。和其他功率半導體(例如絕緣柵雙極電晶體或晶閘管)比較,功率MOSFET的優點是其切換速度快,在低電壓下的高效率。功率MOSFET和IGBT都有隔離的閘體,因此在驅動上比較容易。功率MOSFET的缺點是增益較小,有時閘極驅動的電壓甚至比實際要控制的電壓還低。

MOSFET及互補式金屬氧化物半導體(CMOS)技術持續的演進,自1960年起已用在積體電路上,這也是功率MOSFET的設計得以實現的原因。功率MOSFET和一般信號級的MOSFET原理相同。功率MOSFET常用在電力電子學,是源自信號級的MOSFET,自1970年代開始有商品販售[2]。

功率MOSFET是最常見的功率半導體,原因是因為其閘極驅動需要的功率小、以及快速的切換速度[3]、容易實施的並聯技術[3][4]、高頻寬、堅固性、偏壓簡單、容易使用、也容易維修[4]。在低壓(200V以下)的應用中,功率MOSFET是最常見的功率半導體。功率MOSFET可以用在許多不同的領域中,包括大部份的電源供應器、直流-直流轉換器、低電壓電機控制器等,以及許多其他的應用。

歷史

[編輯]金屬氧化物半導體場效電晶體是貝爾實驗室的Mohamed Atalla和Dawon Kahng在1959年發明的,是電力電子學的一大突破。MOSFET一代一代的推進,讓電力電子元件的設計者可以達到雙極性電晶體無法達到的性能以及功率密度[5]。

日立製作所在1969年發明了第一個垂直式的功率MOSFET[6],之後稱為VMOS(V 型槽MOSFET)[7]。日本産業技術綜合研究所的Y. Tarui, Y. Hayashi和Toshihiro Sekigawa首次提出有自對準閘極的雙擴散MOSFET(DMOS)[8][9]。1974年時,日本東北大學的西澤潤一發明了用在音頻上的功率MOSFET,很就由山葉公司生產,用在高保真音頻功率擴大器。JVC、Pioneer、索尼及東芝也開始在1974年開始生產有功率MOSFET的放大器[10]。Siliconix在1975年開始販售VMOS[7]。

VMOS和DMOS發展成當時所謂的VDMOS(垂直型DMOS)[10]。惠普實驗室John Moll的研突團隊在1977年製作了DMOS的原型,展示DMOS比VMOS優越的特性,包括低導通阻抗以及高崩潰電壓[7]。日立在同一年開發了橫向擴散金屬氧化物半導體(橫向DMOS),屬於平面型的DMOS。日立是1977年至1983年之間,唯一的LDMOS製造商,當時的LDMOS是由HH Electronics和Ashly Audio用在音頻功率擴大器中,也用在音樂以及公共廣播系統中[10]。當2G數位蜂窩網絡在1995年開始使用時,LDMOS廣為使用在2G、3G等無線網絡的無線電功率擴大器中[11],後來也用在4G網絡中[12]。

Alex Lidow於1977年在史丹福大學和Tom Herman共同發明了HexFET,六邊形的功率MOSFET[13][14]。國際整流器公司在1978年開始販售HexFET[7][14]。絕緣柵雙極電晶體(IGBT)結合了功率MOSFET以及雙極性電晶體(BJT)的特點,是由通用電氣的B·賈揚特·巴利加在1977年至1979年所發明的[15]。

超接合面(Super Junction)MOSFET是用P+ columns穿透N-外延層的MOSFET。將P層和N層疊層的概令念最早是由大阪大學的Shozo Shirota和Shigeo Kaneda在1978年提出[16]。飛利浦的David J. Coe發明了超接合面的MOSFET,作法是將p型及n型的層對調,並且因此在1984年申請了美國專利,在1988年通過[17]。

應用

[編輯]功率MOSFET是最常用到的功率半導體[3]。截至2010年[update],功率MOSFET佔功率半導體市場的53%,比絕緣柵雙極電晶體(27%)、射頻功率放大器(11%)及雙極性電晶體(9%)要多[18]。截至2018年[update],每年銷售的功率MOSFET超過五百億個[19],其中包括溝槽式(Trench)功率MOSFET,到2017年二月為止已銷售一百億個[20],以及意法半導體的MDmesh(超接合面MOSFET),截至2019年[update]已販售五十億個[16]。

RF DMOS,也稱為RF功率MOSFET,是設計在射頻(RF)應用的DMOS功率電晶體,用在許多電台廣播及無線電應用中[23][24]

功率MOSFET也常用在運輸技術中[25][26][27],包括許多不同種類的載具。

在汽車產業中[28][29][30],功率MOSFET是常見的汽車電子元件[31][32][21]。

功率MOSFET(包括DMOS、LDMOS及VMOS)也可以用在其他的應用領域中。

基本結構

[編輯]

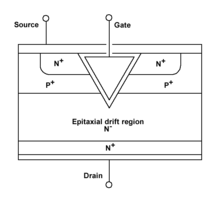

在第一個商用功率半導體問世的1970年代,已研發了許多的結構,不過大部份(至少到目前為止)已不再開發,主要的結構為垂直擴散MOS(VDMOS)結構(也稱為是雙擴散MOS,或DMOS),以及橫向擴散金屬氧化物半導體(LDMOS)結構。

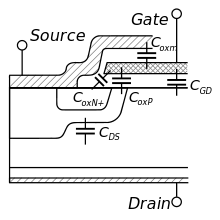

VDMOS的截面(如圖1)可以看出元件的「垂直特性」:可以看出源極電極放在汲極的上方,在電晶體導通時,電流主要是垂直路徑。VDMOS的「擴散作用」是指其製程。P極井(如圖1)是透過擴散過程形成(其實是雙重擴散過程,產生P和N+區,因此稱為雙擴散)。

功率MOSFET和側向MOSFET的結構不同:就像大部份功率元件一樣,其結構是垂直的,不是水平的。在平面結構中,電流和擊穿電壓額定都是通道大小的函數(也就是通道的長和寛),因此在矽晶面積上沒有有效率的使用。在垂直架構中,電晶體的電壓額定是N磊晶摻雜及厚度的函數(可以參考圖1),而電流額定是通道寬度的函數。因此可以讓電晶體在小的矽晶片中,可以維持高截止電壓以及大電流額定。

LDMOS是側向結構的功率MOSFET,主要是用在高端音響放大器[10]以及無線蜂窩網絡(例如2G、3G[11]及4G[12])用的無線電功率放大器 。好處是在飽和區(對應電晶體的線性區)特性比VDMOS好。VDMOS主要用在切換的應用中,只會有開和關二個狀態,不需考慮飽和區的特性。

導通電阻

[編輯]

當功率MOSFET在導通狀態時,在汲極和源極之間有電阻性的行為。在圖2中可以看到電阻(稱為RDSon,表示導通時,在汲極和源極之間的電阻)是以下電阻的和:

- RS是源極電阻。代表了從封裝的端子到MOSFET通道之間的所有電阻:包括打線接合的電阻、源端金屬化的電阻,以及N+井的電阻。

- Rch是通道電阻,和通道寛度成反比。通道電阻是低壓MOSFET中,RDSon的主要貢獻來源,因此有許多的研究是在縮小晶片大小,增加通道密度。

- Ra是接觸電阻,若電阻的方向從水平(通道)變成垂直(到汲極接觸)時,接觸電阻表示在閘極電阻下磊晶區的電阻。

- RJFET是上述尺寸減少造成的不良影響:P注入(如圖1)形成了閘極的寄生JFET電晶體,會減少電流的流動。

- Rn是磊晶層的電阻,磊晶層的作用是維持截止電壓,Rn直接和元件的電壓額定有關。高壓的MOSFET需要較厚,較少摻雜的磊晶層,也就是高電阻,相對的,低壓的MOSFET只需要較薄的磊晶層,但摻雜要比較多,也就是低電阻。因此,Rn是高壓MOSFET中,RDSon的主要貢獻來源。

- RD是汲極電阻,其特性類似RS,代表了電晶體基板的電阻(截面圖是示意圖,未照實際比例,底下的N+層其實是最厚的)以及連接到封裝端子之間的電阻。

崩潰電壓以及導通電阻之間的取捨

[編輯]

在不導通時,功率MOSFET可以等效為PIN二極管(由the P+擴散層、N−磊晶層以及N+基板組成)。在這個高度不對稱的結構逆向偏壓時,無載子的區域會往低摻雜的區域擴展,也就是N−層的上方。表示這一層需要承受不導通時,大部份汲極到源極的電壓。

不過當MOSFET在導通狀態時,N−層沒有功能,而且,因為是低摻雜的區域,其本質電阻無法忽略,會加在導通時的電阻RDSon當中(就是圖2中的電阻Rn)。

二個主要的參數決定了電晶體的崩潰電壓以及RDSon:摻雜程度以及N−磊晶層厚度。磊晶層厚度越厚,摻雜越少,崩潰電壓越高。相反的,磊晶層厚度越薄,摻雜越多,RDSon越低(MOSFET的導通損失也會越少)。因此這是MOSFET設計上的取捨,在電壓額定以及導通電阻之間進行取捨[來源請求],這也是圖3所描述的。

本體二極管

[編輯]在圖1中可以看到,MOSET的工作原理只要源極連接到N+區,但源極的金屬化連接了N+和P+的注入部份。若有這樣的情形出現,會形成在N摻雜源極以及汲極之間的浮動的P區,可以等效為NPN電晶體,有一個未連接的基極。在特定情形下(例如汲極有大電流、汲極到源極的電壓有數伏特的大小),會觸發雜散NPN電晶體,使得MOSFET不可控。P注入層到源極金屬化部份的連接會使雜散電晶體的基極對射極短路(MOSFET的源極),因此不會有了寄生鎖存效應。

不過這解法在MOSFET的汲極(陰極)和源極(陽極)之間產生了二極管(本體二極管,body doide),使其只能單一方向阻隔電流。

在H橋或半橋的電路組態中,若是電感性負載,可以把本體二極管用來作為續流二極管。這些二極管的順向導通壓降會比較高,但可以承受大電流,在許多的應用中已經足夠,而且可以節省元件個數,減少設備的成本以及電路板的大小。

切換特性

[編輯]

功率MOSFET是單載子元件,可以高速進行切換。沒有雙載子元件需要移除少數載子的問題。不過功率MOSFET的切換速度仍有本質上的限制,就是MOSFET中的內部電容(如圖4)。在MOSFET切換時,需要將電容器充電及放電。流進閘極電容的電流會受到外部驅動電路的限制,因此充放電的速度會比較慢。若不考慮功率電路中的電感,驅動電路會主控MOSFET的切換速度。

電容

[編輯]在MOSFET的datasheet中,電容會用Ciss(汲極和源極短路時的輸入電容)、Coss(閘極和源極短路時的輸出電容)、Crss(源極短路到地時的反向傳遞電容)。這些電容和內部電容的關係如下:

其中CGS、CGD和CDS是閘極對源極、閘極對汲極、汲極對源極的電容。供應商選用Ciss、Coss和Crss來標示的原因是可以直接量測。而CGS、CGD和CDS比較接近物理上的意義,條目後續內容也會用此方式說明。

閘極對源極電容

[編輯]閘極對源極電容CGS是由CoxN+、CoxP和Coxm的並聯連接組成(如圖4)。N+和P區都是高度摻雜的區域,這二部份的電容可以視為是常數,Coxm是多晶矽閘極和金屬源極之間的電容,也是常數。因此一般會將CGS視為是常數,不會隨電晶體的狀態而改變。

閘極對汲極電容

[編輯]閘極對汲極電容CGD可以視為二個基本電容串聯後所組成。第一個是氧化層的電容(CoxD),是由閘極電極、二氧化矽以及上方N磊晶層所產生,這個電容是定值。第二個電容(CGDj)是因為MOSFET不導通時,空乏層的擴展所產生,因此和源極及汲極之間的電壓有關。CGD的值為:

空乏層的寬度為[33]

其中是矽的電容率,q是電子電荷,N是摻雜程度。CGDj的值可以用平板電容器的公式來近似:

其中AGD是源極及汲極重疊部份的面積,因此:

可以看出CGDj(以及CGD)的電容值會隨源極及汲極的電壓而改變。若電壓是增加,則電容也會增加。若MOSFET在導通態,CGDj短路,閘極對汲極電容等於CoxD,為一定值。

汲極對源極電容

[編輯]因為源極的金屬化會覆蓋P井(如圖1),汲極和源極的端子會被PN結隔開,因此CDS即為PN結的電容,電容是非線性電容,可以用類似CGDj的公式求得。

其他有關動態響應的元件

[編輯]

包裝電感

[編輯]MOSFET的晶片需要和和外部的電路連接,多半會用打線接合的方式連接到MOSFET的端子(目前也在研究其他的接方式)。接線中會有雜散電感,這不是專門針對MOSFET的技術,但若在高速切換下,會有很明顯的效應。雜散電感會使電流維持定值,在晶體關閉時會產生大電壓,因此會增加切換損。

雜散電感在MOSFET的每一個端子都會出現,其影響不同:

- 閘極電感很小(假設小於數百nF),原因是閘極的電流梯度比較慢,。不過有時閘極電感和電晶體的輸入電容器會產生振盪,可能會產生很大的切換損失,甚至會破壞設備,因此要設法避免。在一般的設計中,會維持雜散電感很低,讓此一現象不會出現。

- 汲極電感會在MOSFET導通時設法減少汲極電壓,因此可以降低切換導通損失(turn-on loss)。不過在關斷MOSFET時也會產生大電壓,因此會增加關斷損失(turn-off loss)。

- 源極雜散電感的行為類似汲極電感,但會加上回授效應,會讓切換持續的時間變長,增加切換損失。

- 在要開始快速開啟時,因為源極雜散電感,晶片上的源極電壓可以快速上昇,閘極電壓也可以快速上昇,而內部的VGS會維持較低的值一段時間,因此會使切換時的導通變慢。

- 在要開始快速關斷時,源極電感上的電流快速減少,上面的電壓會變負值(相對包裝外的導線),因此讓內部的VGS增加,讓MOSFET維持導通,因此切換時的關斷也會變慢。

工作時的限制

[編輯]閘極氧化層崩潰

[編輯]閘極的氧化層很薄(100 nm,甚至更小),因此可以承受的電壓有限。製造商會在資料表中列出閘極-源極電壓的最大值,大約是20 V,若電壓超過此限制值,可能會造成元件的損壞。而且,過高閘極-源極電壓會讓縮短MOSFET的壽命,降低RDSon的效果不明顯,甚至沒有效果。

為了改善這方面的問題,會配合閘極驅動器應用。

最大汲極-源極電壓

[編輯]功率MOSFET在關斷時,汲極-源極電壓有最大值的限制,若電壓超過此限值,會出現突崩潰的情形。若電壓超過崩潰電壓,會讓功率開關誤導通,可能因為誤導通時產生的大量熱量,造成開關或是其他電路的損壞。

最大汲極電流

[編輯]一般而言,功率MOSFET的汲極電流需低於一定值(最大連續汲極電流)。汲極電流可以在短時間超過該限制值,不過仍需要小於最大脈波電流(有時會標示不同的脈波持續時間)。汲極電流會讓內部元件(例如打線接合)因為焦耳加熱而發熱,也和其他現象有關(例如金屬層的電遷移)。

最高溫度

[編輯]為了功率MOSFET元件的可靠度,其結溫(TJ)有最高溫度的限制,此溫度和MOSFET晶片的佈置以及封裝的材料有關。封裝材料的模塑料以及人造樹脂的特性,會元件的最高結溫。

最高工作環境溫度是由發熱量以及熱阻所決定。結點到外殼(junction-to-case)的熱阻是元件以及封裝的固有特性,外殼到環境(case-to-ambient )的熱阻主要和在電路版上的佈局、固定方式、散熱片、氣流或是散熱液體流動有關。

功率MOSFET發熱的方式(連續發熱或是脈衝發熱),會對應不同的熱質量特性,也會會影響最大操作溫度。一般來說,相同發熱量下,若脈波的頻率最低,最高工作環境溫度就可以越高,因為元件可以冷卻的時間比較長。有些模型(例如福斯特電抗定理)可以用來分析功率模組暫態下的溫度特性。

安全工作區

[編輯]安全工作區會結合功率MOSFET的汲極電流以及汲極-源極電壓,定義MOSFET可以正常使用,不會損壞元件的電壓及電流範圍。一般會用圖示的方式,在座標軸分別是汲極電流及汲極-源極電壓的圖上標示。汲極電流以及汲極-源極電壓都需要低於其標示的最大值,而且其乘積也要小於元件可以散熱的最大發熱量。一般來說,功率MOSFET因為散熱能力的限制,無法工作在汲極-源極電壓以及汲極電流均為最大值的條件下[34]。

閂鎖

[編輯]功率MOSFET的等效電路中包括一個MOSFET,以及一個並聯的寄生BJT。此BJT無法透過閘極進行控制,因此若導通了,就無法關閉。此一現象稱為閂鎖,會造成元件的毀壞。BJT可能因為p-type體區的電位差而導通。為了避免閂鎖現象,MOSFET體以及源極之間會透過封裝直接短路,避免有電位差。

技術

[編輯]

佈置

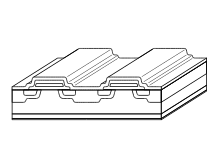

[編輯]Cellular結構

[編輯]如上所述,功率MOSFET可以流過的電流是由其閘極通道的寬度所決定。閘極通道寬度是圖中截面上的Z軸。

為了降低成本以及尺寸,會讓晶片的面積越小越好。因此有許多的最佳化技術可以增加通道的表面積,也就是增加「通道密度」。作法包括在MOSFET晶片產生多個重覆性的Cellular結構。針對這些單元,有提出幾種不同的規劃方式,最著名的是International Rectifier的HEXFET元件使用的六邊形外形。

另外一種增加通道密度的方式是縮小基本結構的尺寸,因此可以在相同的表面積內容納更多的單元,也就增加了通道密度。不過隨着單元尺寸的縮小,要確保每一個單元的接面正常的難度也隨之提高。因此會出現條形結構(如圖所示)。條形結構在通道密度的效率不如Cellular結構,但是其長度可以比較小。平面結構的另一個優點是比較不會因為順向偏壓讓雜散BJT導通產生的突崩潰而失效。在Cellular結構中,若任何一個單元的源極接觸不好,就有可能會出現雜散BJT,進而出現突崩潰。而平面條狀結構的MOSFET,只會因為外部熱應力產生的突崩潰而使其損壞[35]。

結構

[編輯]

P-substrate功率MOSFET

[編輯]P-substrate MOSFET(常簡稱PMOS)是摻雜方式相反的MOSFET(如圖1,但P改為N,N改為P)。MOSFET是由P類的基板構成,有P−的磊晶。通道在N區,晶體是由閘極對源極的逆向電壓導通。這適用於降壓轉換器,開關的一端接在輸入電壓的高電壓側。若是用N-MOSFET,此一組態需要提供的電壓給閘極,但是用P-MOSFET,需要的電壓不會超過。

這類MOSFET的主要缺點是導通特性不佳,因為是利用電洞作為載流子。電洞的載子遷移率比電子要差,而電導率和載子遷移率有關。PMOS元件的會是相同尺寸N-MOSFET的三倍。

VMOS

[編輯]UMOS

[編輯]

此功率MOSFET結構(也稱為trench-MOS),其閘極電極埋在矽蝕刻的溝槽內。因此可以產生垂直型的通道。此結構主要好處是沒有JFET效應。UMOS的名稱是源自其U型的溝槽。

超接合面深溝槽技術(Super-junction deep-trench technology)

[編輯]針對電壓等級超過500V的MOSFET,元件製造商(包括英飛凌科技以及其CoolMOS產品)開始使用電荷補償原理(charge compensation principle)。使用此技術時,磊晶層的電阻(佔高壓MOSFET元件電阻的95%)可以縮小到原來的五分之一。

瑞薩電子為了提昇超接合面(super-junction)MOSFET的生產效率以及可靠度,發展了有深溝槽(deep-trench)製程技術的超接合面結構。此技術是在低雜質的N型材料上饋蝕刻溝槽,以產生P型區。此製程克服了多層磊晶成長時的一些固有問題,其導通電阻及內部電容都很低。

因為超接合面結構的p-n接合面面積增加,相較於傳統平面式的功率MOSFET,超接合面結構MOSFET的逆向恢復時間較短,但逆向恢復電流較大。

相關條目

[編輯]參考資料

[編輯]- ^ IRLZ24N, 55V N-Channel Power MOSFET, TO-220AB package; Infineon.. [2020-09-22]. (原始內容存檔於2018-06-25).

- ^ Irwin, J. David. The Industrial Electronics Handbook. CRC Press. 1997: 218 [2020-09-22]. ISBN 9780849383434. (原始內容存檔於2020-08-03).

- ^ 3.0 3.1 3.2 Power MOSFET Basics (PDF). Alpha & Omega Semiconductor. [29 July 2019]. (原始內容存檔 (PDF)於2020-01-10).

- ^ 4.0 4.1 Duncan, Ben. High Performance Audio Power Amplifiers. Elsevier. 1996: 178–81. ISBN 9780080508047.

- ^ Rethink Power Density with GaN. Electronic Design. 21 April 2017 [23 July 2019]. (原始內容存檔於2020-08-01).

- ^ Oxner, E. S. Fet Technology and Application. CRC Press. 1988: 18 [2020-09-23]. ISBN 9780824780500. (原始內容存檔於2019-12-30).

- ^ 7.0 7.1 7.2 7.3 Advances in Discrete Semiconductors March On. Power Electronics Technology (Informa). September 2005: 52–6 [31 July 2019]. (原始內容存檔 (PDF)於2006-03-22).

- ^ Tarui, Y.; Hayashi, Y.; Sekigawa, Toshihiro. Diffusion Self-Aligned MOST; A New Approach for High Speed Device. Proceedings of the 1st Conference on Solid State Devices. September 1969 [2020-09-23]. doi:10.7567/SSDM.1969.4-1. (原始內容存檔於2020-09-13).

- ^ McLintock, G. A.; Thomas, R. E. Modelling of the double-diffused MOST's with self-aligned gates. 1972 International Electron Devices Meeting. December 1972: 24–26. doi:10.1109/IEDM.1972.249241.

- ^ 10.0 10.1 10.2 10.3 Duncan, Ben. High Performance Audio Power Amplifiers. Elsevier. 1996: 177–8, 406. ISBN 9780080508047.

- ^ 11.0 11.1 Baliga, B. Jayant. Silicon RF Power MOSFETS. World Scientific. 2005 [2020-09-23]. ISBN 9789812561213. (原始內容存檔於2019-12-18).

- ^ 12.0 12.1 Asif, Saad. 5G Mobile Communications: Concepts and Technologies. CRC Press. 2018: 134 [2020-09-23]. ISBN 9780429881343. (原始內容存檔於2020-08-06).

- ^ SEMI Award for North America. SEMI. [5 August 2016]. (原始內容存檔於2016-08-05).

|url-status=和|dead-url=只需其一 (幫助) - ^ 14.0 14.1 International Rectifier's Alex Lidow and Tom Herman Inducted Into Engineering Hall of Fame. Business Wire. 14 September 2004 [31 July 2019]. (原始內容存檔於2019-07-31).

- ^ Baliga, B. Jayant. The IGBT Device: Physics, Design and Applications of the Insulated Gate Bipolar Transistor. William Andrew. 2015: xxviii, 5–11 [2020-09-23]. ISBN 9781455731534. (原始內容存檔於2020-08-06).

- ^ 16.0 16.1 MDmesh: 20 Years of Superjunction STPOWER MOSFETs, A Story About Innovation. STMicroelectronics. 11 September 2019 [2 November 2019]. (原始內容存檔於2019-11-02).

- ^ US Patent 4,754,310

- ^ Power Transistor Market Will Cross $13.0 Billion in 2011. IC Insights. June 21, 2011 [15 October 2019]. (原始內容存檔於2019-10-15).

- ^ Carbone, James. Buyers can expect 30-week lead times and higher tags to continue for MOSFETs (PDF). Electronics Sourcing. September–October 2018: 18–19 [2020-10-04]. (原始內容存檔 (PDF)於2020-10-25).

- ^ Williams, Richard K.; Darwish, Mohamed N.; Blanchard, Richard A.; Siemieniec, Ralf; Rutter, Phil; Kawaguchi, Yusuke. The Trench Power MOSFET: Part I—History, Technology, and Prospects. IEEE Transactions on Electron Devices. 23 February 2017, 64 (3): 674–691. Bibcode:2017ITED...64..674W. doi:10.1109/TED.2017.2653239.

- ^ 21.0 21.1 MOSFET. Infineon Technologies. [24 December 2019]. (原始內容存檔於2020-11-05).

- ^ Infineon EiceDRIVER gate driver ICs (PDF). Infineon. August 2019 [26 December 2019]. (原始內容存檔 (PDF)於2020-08-09).

- ^ RF DMOS Transistors. STMicroelectronics. [22 December 2019]. (原始內容存檔於2020-05-14).

- ^ AN1256: Application note – High-power RF MOSFET targets VHF applications (PDF). 意法半導體. July 2007 [22 December 2019]. (原始內容存檔 (PDF)於2020-10-25).

- ^ Emadi, Ali. Handbook of Automotive Power Electronics and Motor Drives. CRC Press. 2017: 117 [2020-10-04]. ISBN 9781420028157. (原始內容存檔於2022-04-10).

- ^ Infineon Solutions for Transportation (PDF). Infineon. June 2013 [23 December 2019]. (原始內容 (PDF)存檔於2022-03-19).

- ^ HITFETs: Smart, Protected MOSFETs (PDF). Infineon. [23 December 2019]. (原始內容存檔 (PDF)於2020-10-06).

- ^ CMOS Sensors Enable Phone Cameras, HD Video. NASA Spinoff. NASA. [6 November 2019]. (原始內容存檔於2020-12-14).

- ^ Veendrick, Harry J. M. Nanometer CMOS ICs: From Basics to ASICs. Springer. 2017: 245 [2020-10-04]. ISBN 9783319475974. (原始內容存檔於2022-04-10).

- ^ Korec, Jacek. Low Voltage Power MOSFETs: Design, Performance and Applications. Springer Science+Business Media. 2011: 9–14. ISBN 978-1-4419-9320-5.

- ^ Automotive Power MOSFETs (PDF). Fuji Electric. [10 August 2019]. (原始內容存檔 (PDF)於2020-10-29).

- ^ Williams, R. K.; Darwish, M. N.; Blanchard, R. A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The Trench Power MOSFET—Part II: Application Specific VDMOS, LDMOS, Packaging, Reliability. IEEE Transactions on Electron Devices. 2017, 64 (3): 692–712. Bibcode:2017ITED...64..692W. ISSN 0018-9383. doi:10.1109/TED.2017.2655149.

- ^ Simon M. Sze, Modern semiconductor device physics, John Wiley and Sons, Inc 1998 ISBN 0-471-15237-4

- ^ Pierre Aloïsi, Les transistors MOS de puissance in Interrupteurs électroniques de puissance, traite EGEM, under the direction of Robert Perret, Lavoisier, Paris, 2003 [in French] ISBN 2-7462-0671-4

- ^ 存档副本 (PDF). [2020-11-29]. (原始內容存檔 (PDF)於2020-10-20).

- ^ Duncan A. Grant, John Gowar POWER MOSFETS: Theory and Applications John Wiley and Sons, Inc ISBN 0-471-82867-X , 1989

延伸閱讀

[編輯]- "Power Semiconductor Devices", B. Jayant Baliga, PWS publishing Company, Boston. ISBN 0-534-94098-6